すべてのカテゴリを見る

チップテスト

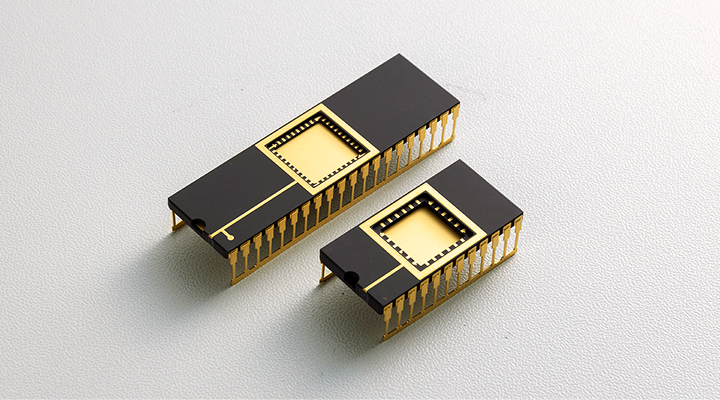

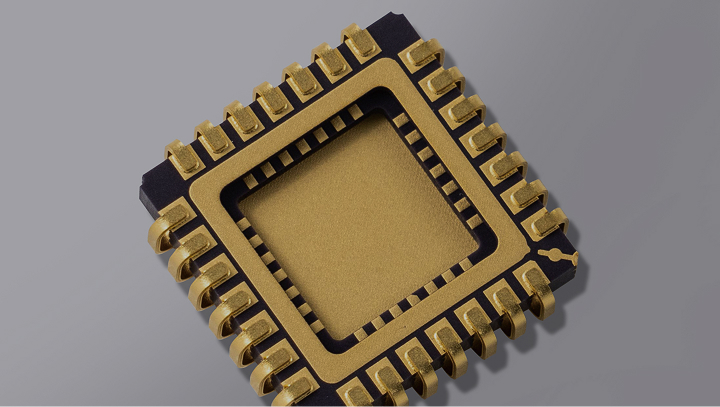

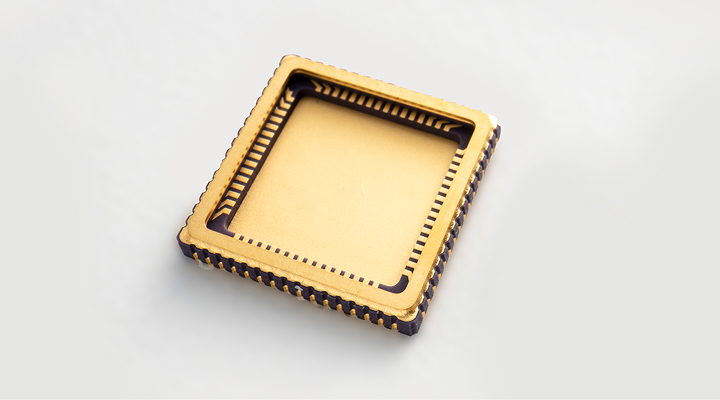

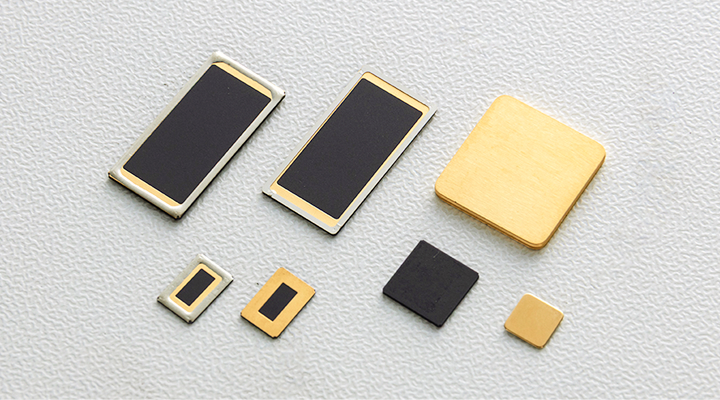

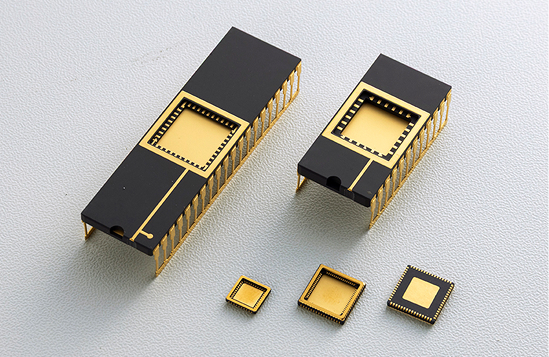

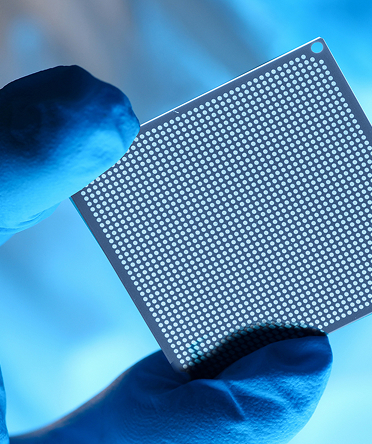

半導体デバイスのウェハテスト後に行われるバーンイン試験・最終テスト・特性評価(デバッグ)では、チップを正確に保持し、テスターとの安定した接続を実現するための高性能パッケージが求められます。

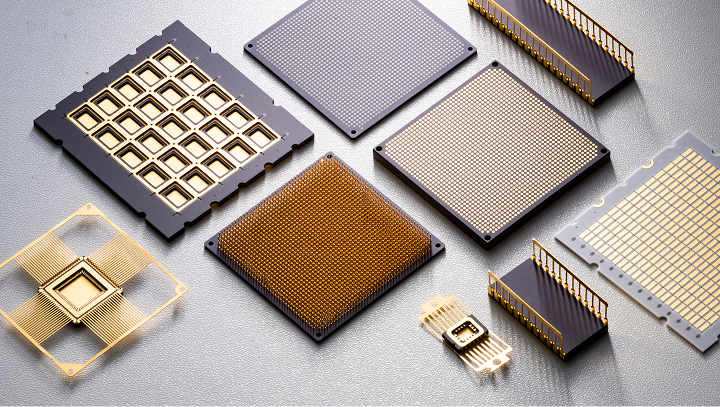

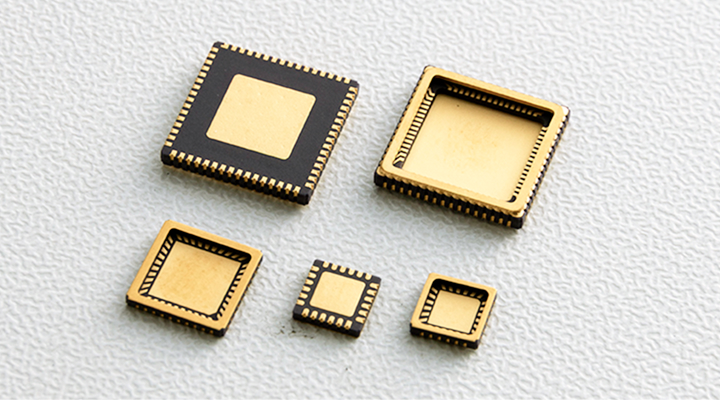

NTKセラミックのセラミックパッケージ/セラミック基板は、チップテストに特化した高周波特性・熱安定性・寸法精度・高耐久性を備え、先端半導体の評価工程を高い信頼性で支えています。超低誘電率・低誘電正接を特徴とするセラミック材料は、GHz帯高速信号の品質を損なわずに伝送できるため、AIアクセラレータ、CPU/GPU、高速LSIなどの性能評価に最適。

さらに、高熱伝導性・耐熱性・低熱膨張率により、過酷なバーンイン条件でも安定した動作を維持し、繰り返し使用されるテスト用途において長寿命・高耐久パッケージとして信頼されています。

- 用途・活用分野

-

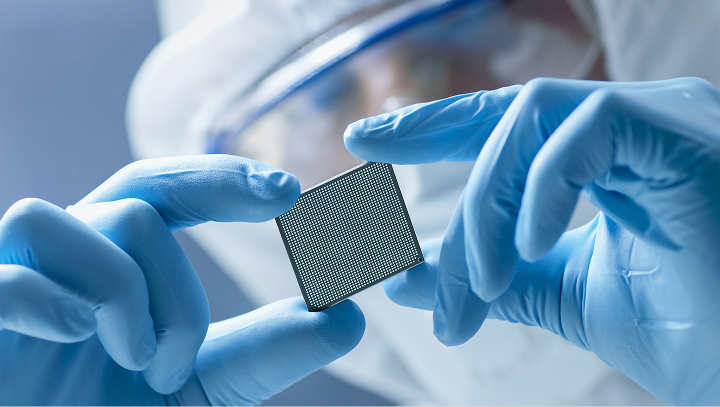

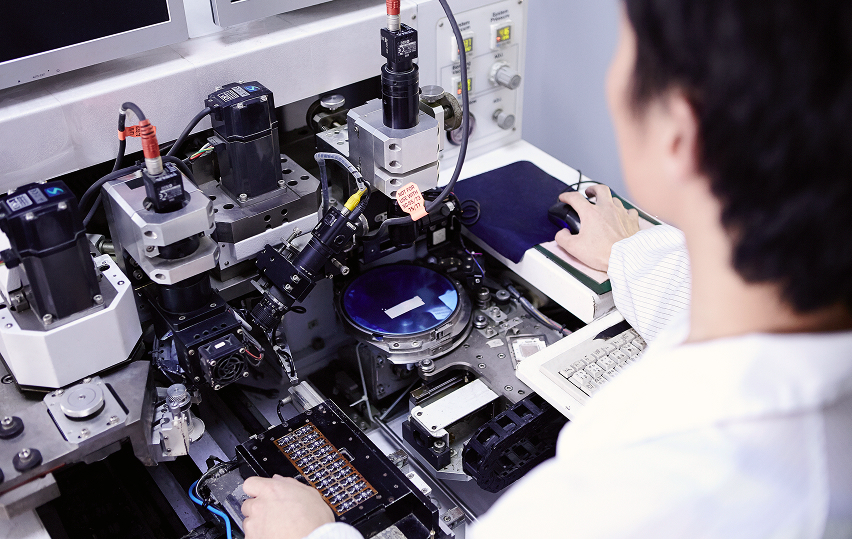

チップテストの工程では、デバイスの品質・歩留まりを左右するため、パッケージ側には高精度・高再現性のテスト環境が求められます。

近年はAI・高速通信・データセンター向け半導体の複雑化により、テスト基板にも高周波対応・高密度化・高放熱構造が不可欠となっています。

NTKセラミックは、こうした要求に応える高信頼パッケージを提供し、先端チップの高精度評価を長期間支えています。主な用途

- チップテスト

製品の特徴と強み

-

- 1. 高速チップテストを支える“超低損失・高再現性”信号伝送

- GHz帯で動作する半導体デバイスのテストでは、測定機器へ高速信号を劣化なく伝送することが必須です。

セラミックパッケージは、超低誘電率・低誘電正接を備え、信号損失・反射・クロストークを最小化。

AIチップや高性能プロセッサのように高速信号処理を行うデバイスでも、テスト結果の再現性・測定精度を高いレベルで確保します。

信号品質、低ノイズ、高周波安定性を兼ね備えることで、デバッグ効率の向上・評価時間の短縮にも貢献します。

-

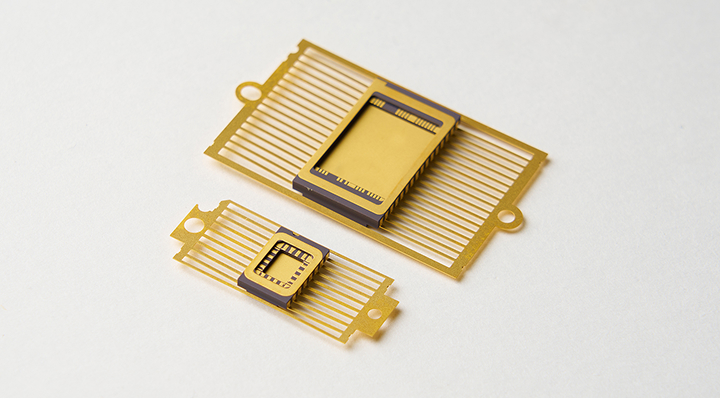

- 2. 高温負荷テストに耐える放熱性・熱安定性・長寿命構造

- チップテストでは、デバイスを高温で長時間動作させるバーンイン試験が欠かせません。

セラミックパッケージは、高熱伝導率による温度ドリフト抑制、低熱膨張係数による応力低減、125°C以上の高温環境でも劣化しない耐熱性・耐久性を兼ね備え、厳しい熱環境下でも安定した測定条件を維持します。

また、繰り返しの温度サイクルでも変形しにくく、テスト工程での長期利用に適した高耐久・長寿命パッケージとして機能します。

-

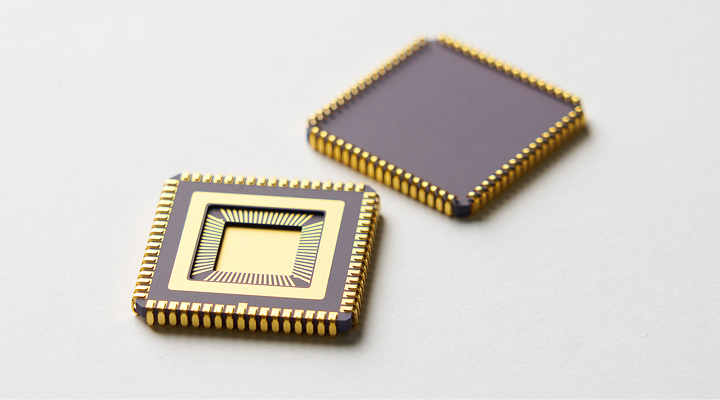

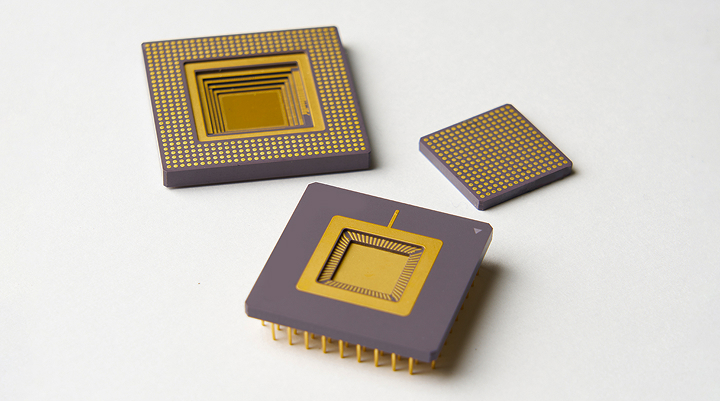

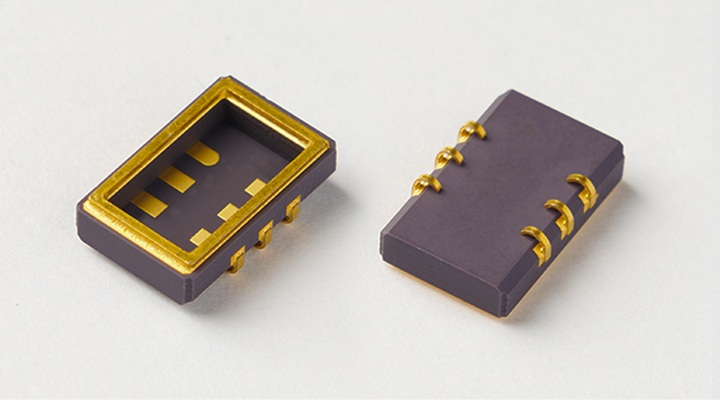

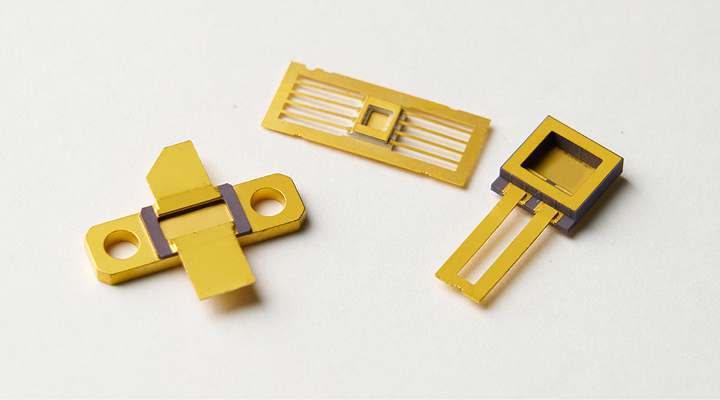

- 3. 多端子接続を支える精密構造と高密度多層技術

- テストソケットやプローブカードでは、数百〜数千本の端子をミクロンレベルの精度で確実に接触させる必要があります。

セラミックの高剛性、安定性により、繰り返しのテスト負荷や高温下でも位置ずれや変形を防止し、接触信頼性を長期間維持します。

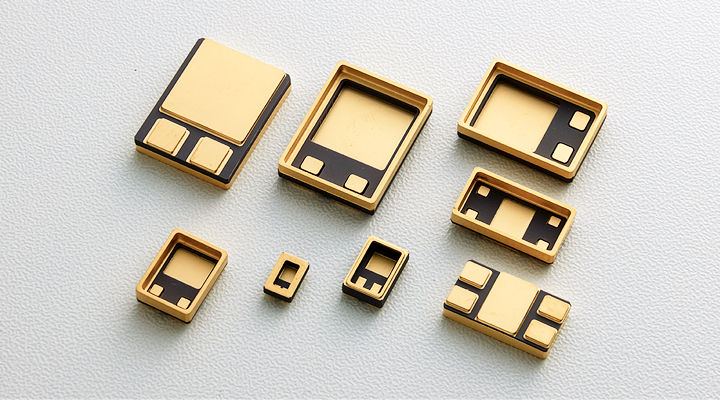

さらに、HTCC技術による多層配線、高密度、高耐熱、高放熱性により、複雑な評価環境をパッケージ内部で完結できるため、次世代半導体のテスト精度向上に大きく貢献します。

- 次世代への取り組み

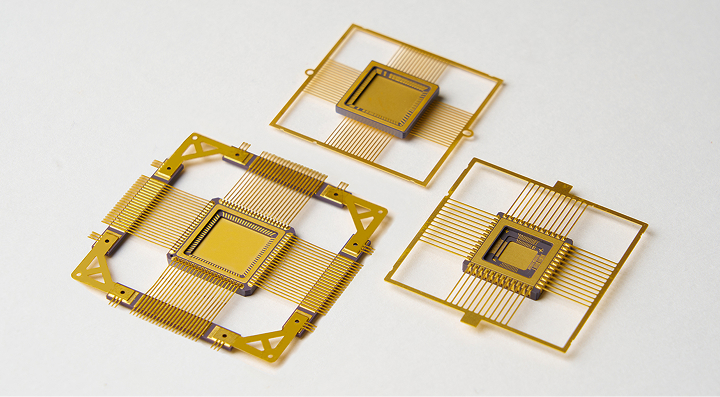

- 半導体デバイスの高速化・高出力化に伴い、チップテストパッケージにはさらなる高周波対応・放熱性向上・高精度化が求められています。

NTKセラミックは、低誘電材料や高熱伝導セラミック、多層配線技術、金属とのハイブリッド構造など、

次世代テスト環境に向けたパッケージ開発を積極的に推進しています。

これにより、AI・データセンター・車載・通信分野など、多様な先端半導体の測定精度・評価再現性・信頼性向上に貢献し、未来の半導体品質を支える基盤技術として進化し続けます。

-

ご相談・カスタム対応

-

お客様のご使用方法及び基本要求をベースに

セラミックパッケージの構造・デザインを個別にご提案「特殊な形状でも対応できるか?」「要求する特性にミートできるか?」「デザインルール外でも対応できるか?」など、個別の技術課題にも柔軟に対応いたします。ぜひお気軽にご相談ください。